# ECO32 User Manual

Martin Geisse

#### CHAPTER 1

# Introduction

The ECO32 is a general-purpose 32-bit RISC soft-core microprocessor, to be implemented on an FPGA. It was originally designed to understand the RISC architecture as described by Hennessy and Patterson in their books. The current version is a simple, albeit slow implementation of the instruction set architecture described in this manual. Future versions will include various optimizations to make the ECO32 feasible for real-world projects.

#### 1. Features

The ECO32 supports the following features:

- Soft-core processor to be implemented on an FPGA

- 32 general-purpose registers, each 32 bits wide

- 32-bit ALU, shifter, multiplication and division units

- load/store architecture

- 32-bit unified instruction and data address space

- 16 external interrupt lines

- two privilege modes to execute both trusted and untrusted code

- paged virtual memory with a page size of 4K

- assembler, instruction-set simulator, and C compiler support

#### 2. Requirements

So far, the ECO32 has only been implemented on a Xilinx Spartan-3 FPGA. Implementing it on other FPGAs may cause problems if the ECO32 uses device primitives that are not supported on the target platform.

#### CHAPTER 2

# ECO32 Architecture

The ECO32 is a general-purpose 32-bit RISC processor. Its instruction set is tailored to handle only the most basic computation steps at once, and to allow arbitrary combination of these basic steps for full flexibility. Instructions are executed sequentially. The ECO32 also includes the basic mechanisms to implement modern operating systems, such as interrupts, privileged instructions, and virtual memory. Operations on floating-point data types are not supported.

The ECO32 is a soft-core that must be used in a larger system-on-chip (SoC) design inside a field programmable gate array (FPGA). The ECO32 is connected to other on-chip resources using a uniform SoC bus architecture. These resources include a RAM controller, a ROM controller, and peripheral devices such as coprocessors, communication controllers, and controllers for external devices.

## 1. Data Types

The following basic data types are processed by the ECO32:

- Byte: A unit of 8 bits

- Half-Word: A unit of 16 bits

- Word: A unit of 32 bits

The bits of each unit are written down starting from the most-significant bit to the least significant bit.

The size of the basic units allows the arrangement of bytes as half-words, or of bytes or half-words as words. Two common kinds of arrangements are defined for sequences of bytes or half-words. Let  $a = (a_7, ..., a_0)$ ,  $b = (b_7, ..., b_0)$ ,  $c = (c_7, ..., c_0)$ , and  $d = (d_7, ..., d_0)$  be byte values, and  $p = (p_{15}, ..., p_0)$  and  $q = (q_{15}, ..., q_0)$  be half-word values.

- Big Endian arrangement maps

- the byte sequence (a, b) to the half-word  $(a_7, ..., a_0, b_7, ..., b_0)$ ,

- the byte sequence (a, b, c, d) to the word

- $(a_7,...,a_0,b_7,...,b_0,c_7,...,c_0,d_7,...,d_0)$ , and

- the half-word sequence (p,q) to the word  $(p_{15},...,p_0,q_{15},...,q_0)$ .

- Little Endian arrangement maps

- the byte sequence (a, b) to the half-word  $(b_7, ..., b_0, a_7, ..., a_0)$ ,

- the byte sequence (a,b,c,d) to the word

- $(d_7,...,d_0,c_7,...,c_0,b_7,...,b_0,a_7,...,a_0)$ , and - the half-word sequence (p,q) to the word  $(q_{15},...,q_0,p_{15},...,p_0)$ .

When units of several bits are interpreted as numbers, two different schemes are used. An unsigned interpretation maps the bits  $(a_N,...,a_0)$  to the number  $\sum_{i=0}^N a_i 2^i$ . A signed (or two's complement) interpretation maps the same bit sequence to the number  $-a_N 2^N + \sum_{i=0}^{N-1} a_i 2^i$ .

The functions *signed* and *unsigned* shall denote signed and unsigned interpretation of a bit sequence as a number, respectively.

A bit sequence  $(a_N,...,a_0)$  is truncated to  $M \leq N$  bits by taking the bit sequence  $(a_M,...,a_0)$ . The same bit sequence is zero-extended to  $P \geq N$  bits by taking  $(0,...,0,a_N,...,a_0)$ , or sign-extended to P bits by taking  $(a_N,...,a_N,a_{N-1},...,a_0)$ . Zero-extension and sign-extension preserve the unsigned or signed interpretation, respectively, if the value can be represented in the target number of bits at all.

The function  $truncate_N$  shall denote truncation to N bits,  $zeroext_N$  shall denote zero-extension to N bits, and  $signext_N$  shall denote sign-extension to N bits.

#### 2. Addresses

An address is a 32-bit unsigned value that indicates a location in RAM, ROM, or in a peripheral device. An address is half-word-aligned if it is divisible by 2, that is, its least significant bit is 0. An address is word-aligned if it is divisible by 4, that is, its two least significant bits are 0. The design of the ECO32 ensures that all accesses to the RAM, ROM, or to peripheral devices are aligned with respect to the transferred data size.

The ECO32 distinguishes *virtual* and *physical* addresses. Virtual addresses are generated by a program to address RAM or device locations. Virtual addresses are converted to physical addresses by the memory management unit. Finally, physical addresses select locations in RAM, ROM, or peripheral devices. See Chapter 2, Section ?? for details.

The mapping is always defined in such a way that a virtual address is half-word (word) aligned if and only if the corresponding physical address is. Any attempt to access a half-word (word) sized location at an address that is not half-word (word) aligned is called a *misaligned* access and triggers a fault.

Each physical address in the range 0x00000000 through 0x2FFFFFFF selects a byte-sized location in RAM or ROM. Each half-word (word) aligned address in that range selects a half-word (word) in RAM or ROM comprising the corresponding byte locations in a big-endian fashion.

Each word-aligned physical address in the range 0x30000000 through 0x3FFFFFFF selects a word-sized location in a peripheral device. Byte or half-word sized access to peripheral devices is not allowed and the effect of such accesses on the device and on values read is undefined.

Physical addresses in the range 0x40000000 through 0xFFFFFFF are not used.

# 3. Program Counter (PC)

The PC is a 32-bit virtual address register that contains the address of the next instruction to execute. Each instruction is 32 bits, or 4 bytes wide. An instruction is *fetched* by loading a word value from the virtual address given by the PC, then incrementing it by 4 (thus moving to the next instruction). If the execution of the instruction later modifies the PC, it is this new value that is modified.

#### 4. General-Purpose Registers

Most data processing occurs in a set of 32 general-purpose registers, each 32 bits wide. Instructions exist to perform arithmetic operations, logic operations, multiplication and division, and data type conversion. Such operations load the

operands from general-purpose registers, perform the computation, and store the result back in a general-purpose register. General-purpose registers also hold the addresses and data for transfers to and from RAM, ROM, and peripheral devices. The interpretation of a value in a general-purpose register as data or address depends solely on the instructions that operate on that value – the value itself is an untyped 32-bit unit.

Some general-purpose registers have a special function in addition to their regular behaviour:

- Register #0 is not actually backed by a physical register. Reading from this register always yields the value 0. Writing to this register has no effect. Register #0 can be exploited in various cases where a value of zero is needed in a register, without first loading that value into a register.

- Registers #1 through #29 do not serve any special purpose.

- Register #30 is used to store the return address when an exception occurs. That value is later used by the exception service routine to return to the place where the exception had occurred. At any time when interrupts are enabled, this register may not be used, because its value could be overwritten by an unexpected interrupt.

- Register #31 is used to store the return address in a subroutine call.

## 5. Load/Store Architecture

Specific instructions exist to transfer data to or from RAM, ROM, or peripheral devices. No such data transfer occurs except for these instructions, as well as instruction fetching itself. That is, all other instructions operate entirely inside the  $\rm ECO32$ .

A *load* instruction transfers data from an external source into a general-purpose register. A *store* instruction transfers data from a general-purpose register to an external target. The virtual address of the external source or target is determined by taking the value of a general-purpose register and adding a constant value that is encoded into the instruction.

Load and store instructions come in variants of word, half-word, and byte transfers with respect to the size of the transferred data. The address computation is not affected by the transfer size, but the resulting address must be aligned to the transfer size. A word transfer affects a full 32-bit general purpose register. A half-word or byte store instruction transfers only the lower 16 or 8 bits, respectively. An unsigned half-word load instruction loads 16 bits from an external source, zero-extends it to 32 bits, and stores the result in a general-purpose register. Similarly, a signed half-word load instruction sign-extends the value to 32 bits. Byte-sized load instructions work analogously.

#### 6. Special-Purpose Registers

The ECO32 contains a set of special-purpose registers that are not used for computation, address generation, or data transfer. Instead, these registers control operation of the processor itself. Special purpose registers are accessed with the MVFS and MVTS instructions.

The following special-purpose registers are present in the ECO32:

| Index | Name            |

|-------|-----------------|

| 0     | PSW             |

| 1     | TLB Index       |

| 2     | TLB Entry High  |

| 3     | TLB Entry Low   |

| 4     | TLB Bad Address |

The first special register is the processor status word (PSW). This register contains the main control parameters for the processor. See Chapter 2, Section ?? for details. The PSW can only be accessed from Kernel Mode.

The remaining special-purpose registers are used to communicate with the memory management unit. See Chapter 2, Section ?? for details. The MMU registers can only be accessed from Kernel Mode.

# 7. Processor Status Word (PSW)

The PSW controls execution in various way. It is actually a collection of fields, each of which has its own purpose and effect:

| Bit Index | Name  | Meaning                            |

|-----------|-------|------------------------------------|

| 3128      | _     | (ignored)                          |

| 27        | V     | Exception Service Routine Vector.  |

| 26        | $U_C$ | Current privilege mode.            |

| 25        | $U_P$ | Previous privilege mode.           |

| 24        | $U_O$ | Old privilege mode.                |

| 23        | $I_C$ | Current global interrupt enable.   |

| 22        | $I_P$ | Previous global interrupt enable.  |

| 21        | $I_O$ | Old global interrupt enable.       |

| 2016      | EID   | Exception identifier.              |

| 150       | IEN   | Channel-specific interrupt enable. |

- **7.1. Exception Service Routine Vector.** The V bit of the PSW specifies the address of the exception service routines. If the V bit is 0, then service routines are located at a high physical address that lies at the beginning of the ROM. If the V bit is 1, then service routines are located at a low physical address that lies at the beginning of the RAM. See Chapter 2, Section ?? for details.

- **7.2. Privilege Modes.** The  $U_C$ ,  $U_P$ , and  $U_O$  bits of the PSW form a three-level stack, with  $U_C$  at the top. A bit value X is *pushed on* that stack by the following sequence:

$$U_O \leftarrow U_P$$

$$U_P \leftarrow U_C$$

A value is *popped off* the stack by the following sequence:

$$U_C \leftarrow U_P$$

$$U_P \leftarrow U_O$$

Only  $U_C$  affects execution directly. If  $U_C$  is 0, then the ECO32 runs in Kernel Mode and can access privileged instructions and privileged addresses. If  $U_C$  is 1, then the ECO32 runs in  $User\ Mode$ , and any attempt to access a privileged instruction or privileged address will result in a  $Privileged\ Instruction\ Fault$  or  $Privileged\ Address\ Fault$ , respectively. When any exception is accepted, a value of

0 is pushed onto the three-level stack to enter  $Kernel\ Mode$ , and  $U_O$  is discarded. The RFX instruction pops the topmost value off the stack to restore the execution state before the exception.

A privileged address is any virtual address in the range 0x80000000 through 0xFFFFFFF. This range is reserved for the operating system, and includes both a page-mapped range from 0x80000000 through 0xBFFFFFFF, and a direct-mapped range from 0xC0000000 through 0xFFFFFFF. See Chapter 2, Section ?? for details.

**7.3. Interrupt Enable.** The  $I_C$ ,  $I_P$ , and  $I_O$  bits of the PSW form a three-level stack, with  $I_C$  at the top. A bit value X is *pushed on* that stack by the following sequence:

$$I_O \leftarrow I_P$$

$$I_P \leftarrow I_C$$

$$I_C \leftarrow X$$

A value is *popped off* the stack by the following sequence:

$$I_C \leftarrow I_P \\ I_P \leftarrow I_O$$

Only  $I_C$  affects execution directly. If  $I_C$  is 0, then interrupts are globally disabled. If any device signals an interrupt while  $I_C$  is 0, then admission of that interrupt is postponed. If  $I_C$  is 1, then interrupts are globally enabled (note that interrupts may still be disabled on a per-channel basis, see below). When any exception is accepted, a value of 0 is pushed onto the three-level stack to disable all interrupts, and  $I_C$  is discarded. The RFX instruction pops the topmost value off the stack to restore the execution state before the exception.

The IEN field controls admission of interrupts on a per-channel basis. An interrupt is only accepted if both the global  $I_C$  and the corresponding bit of the IEN are set. Otherwise, admission of the interrupt is postponed until this condition arises. An interrupt may be overlooked if the device negates the interrupt signal again before  $I_C$  and the corresponding IEN bit are both set.

**7.4. Exception Identifier.** When an exception is accepted, the *EID* field of the PSW is loaded with a number that identifies the cause of the exception. The meaning of these numbers is defined in the following table:

| Value | Meaning                                 |

|-------|-----------------------------------------|

| 015   | Device Interrupt 015                    |

| 16    | Bus Timeout                             |

| 17    | Illegal Instruction                     |

| 18    | Privileged Instruction                  |

| 19    | Division by Zero                        |

| 20    | Trap Instruction                        |

| 21    | TLB Miss                                |

| 22    | TLB Write                               |

| 23    | TLB Invalid                             |

| 24    | Illegal Address                         |

| 25    | Privileged Address                      |

| 2631  | (unused - never loaded by the hardware) |

#### 8. Exceptions: Interrupts and Faults

An *Exception* is a control transfer from user code to operating system code. There are two kinds of exceptions: An *Interrupt* occurs when a peripheral device needs the attention of the ECO32. A *Fault* occurs when the execution of an instruction fails.

Interrupts are only accepted between the execution of two instructions, and only if the  $I_C$  and IEN fields of the PSW allow so (see Chapter 2, Section ??). Operating system code can control these fields to disable interrupts during time-critical code sequences or to achieve mutual exclusion. Typically, the interrupt service routine communicates with the device that caused the interrupt, then returns to the interrupted code and continues its execution as if nothing had happened (except that register #30 had been overwritten, see below). Register #30 should not be used for computations, since it would lose its value during an unexpected interrupt.

Faults occur during the execution of an instruction. Typically, a fault service routine would either correct the problem and restart the failed instruction, or terminate the corresponding program. In certain cases, a fault indicates a voluntary control transfer to the operating system to perform some action on behalf of the user program. In that case, the fault service routine would not restart the faulting instruction, but return to the instruction immediately following it.

- **8.1.** Accepting an Exception. When an exception is accepted, the following steps are taken automatically by the ECO32:

- (1) Store the return address in the general-purpose register #30. For interrupts (which occur between two instructions), this is the address of the instruction directly following the occurence of the interrupt. For faults, this is the address of the faulting instruction. Note that although fetching the faulting instruction had already increased the PC by 4, a fault subtracts 4 again to obtain the original address of that instruction.

- (2) Push 0 on the  $(I_C, I_P, I_O)$  stack in the PSW to disable interrupts, and to remember the previous interrupt enable state.

- (3) Push 0 on the  $(U_C, U_P, U_O)$  stack in the PSW to enter Kernel Mode, and to remember the previous privilege mode.

- (4) Set the *EID* field of the PSW to the corresponding exception identifier (see Chapter 2, Section ??)

- (5) Load the address of the service routine into the PC register (see Chapter 2, Section ??)

- 8.2. Exception Service Routine Addresses. The address of the exception service routine, that is, the value loaded into the PC, is determined as follows. First, a base address is computed depending on the value of the V field of the PSW. If the V bit is 0, then the base address is E0000000. If the V bit is 1, then the base address is C0000000. Since these addresses are loaded into the PC, they are virtual. With V set to 0, the address is a direct-mapped address that denotes the physical address 0x20000000, i.e. the first address associated with the ROM. With V set to 1, the address is a direct-mapped address that denotes the physical address 0x00000000, i.e. the first address associated with the RAM. The V bit can therefore be used to handle exceptions in a service routine located in ROM directly after startup, as well as handle them in a service routine located in RAM once an operating system is loaded.

Next, the cause of the exception is inspected. One specific kind of fault, the User Space TLB Miss, is given special treatment. For this fault, the actual address of the service routine is (base address + 8). For all other faults, as well as for all interrupts, the address of the service routine is (base address + 4). This leaves only enough space for a single instruction at (base address + 4), which is therefore typically a jump instruction. The special treatment for User Space TLB misses allows very fast handling of such faults.

- **8.3. Returning Control.** The exception service routine of the operating system can then handle the exception. When the service routine is finished, it typically returns control:

- An interrupt service routine would return to the saved address in register #30 to continue the interrupted code.

- A fault service routine that has corrected a problem with the faulting instruction would reutrn to the saved address in register #30 to restart that instruction.

- A fault service routine that could not correct the problem would not return control. What happens in that case depends on the operating system architecture.

- A fault service routine that performs an action on behalf of a user code request would not return to the faulting instruction, but to the instruction immediately following it. This can be achieved by adding 4 to register #30 before returning.

A single instruction called RFX (return from exception) handles all these cases. This instruction performs the following sequence:

- (1) Load the value in register #30 into the PC.

- (2) Restore the remembered state of the interrupt enable flag and privilege mode by popping the top value off the  $(I_C, I_P, I_O)$  and  $(U_C, U_P, U_O)$  stacks.

# 9. Memory Management Unit (MMU)

All addresses generated by the ECO32, including both the PC as well as those from load and store instructions, are *virtual* addresses. These addresses are transformed to *physical* addresses by the memory management unit (MMU). The physical addresses are finally sent over the SoC bus to the memory controller or to peripheral hardware.

The memory management unit (MMU) distinguishes two parts of the virtual address space and uses different mapping algorithms for them. The page-mapped space ranges from virtual address 0x00000000 through 0xBFFFFFFF. The direct-mapped space ranges from virtual address 0xC0000000 through 0xFFFFFFFF. Note that this leaves the direct-mapped space entirely in the range of privileged addresses, such that only operating system code can access direct-mapped addresses.

**9.1. Direct-Mapped Space.** Virtual addresses in the direct-mapped space are transformed to physical addresses by subtracting the start address of that space, 0xC0000000. Thus, the direct-mapped space can be used to directly access any RAM, ROM, or device location in the physical address space.

**9.2.** Page-Mapped Space. Virtual addresses in the page-mapped space are subdivided into blocks of 4096 bytes called *pages*. Each page is a continuous range of 4096 virtual addresses, and is mapped to a continuous range of 4096 physical addresses called a *page frame*. Both pages and page frames are aligned to their size. Thus, in the page-mapped space, the upper 20 bits of the physical address (the *page frame number*) are computed through a mapping function from the upper 20 bits of the virtual address (the *page number*), and the 12 lower bits of the physical address are directly taken from the 12 lower bits of the virtual address.

The mapping function from pages to page frames can be defined and implemented freely by the operating system. No overall representation of the mapping is implemented by the ECO32 itself. Specifically, the ECO32 does not have a notion of a page table as found in other architectures. Instead, the mapping of pages to page frames is defined by a software function implemented by the operating system, and the results of that function are cached in a special memory called the translation look-aside buffer (TLB).

**9.3.** Translation Lookaside Buffer (TLB). The TLB is a table of 32 entries, each mapping a 20-bit page number to a 20-bit page frame number. Both numbers are stored in an entry. When accessing a page-mapped virtual address, the TLB is searched for the page number. If an entry is found, then its page frame number is concatenated with the 12-bit page local address to yield the physical address. It is an error to have two entries with the same virtual page number, and the result of the mapping is undefined in that case. Having two entries with the same physical page number is fine however, and can be used to *mirror* a physical page frame at multiple virtual pages.

A full page mapping function is defined by  $(2^{20} - 2^{18})$  mappings of pages to page frames. The 32 TLB entries contain a subset of these mappings, preferably those that are most needed in the near future. By writing to the TLB, a different subset can be loaded. It is also possible to change the mapping function itself by removing (overwriting) the old TLB entries and filling in the mappings of the new function. The ECO32 is not concerned with the notion of the overall mapping function, but simply searches the TLB for a matching page number.

Each TLB entry always contains a mapping from a virtual page to a physical page frame. However, entries can be effectively *blanked* by entering a never-occuring page number. For example, virtual addresses in the range 0xC0000000 through 0xFFFFFFF are direct-mapped, and thus never occur as virtual addresses in a TLB lookup.

In no entry is found in a lookup, a TLB Miss Fault occurs. This is either a User Space TLB Miss if the virtual address is in the range 0x000000000 through 0x7FFFFFFF (that is, it is an unprivileged address), or a Kernel Space TLB Miss if the virtual address is in the range 0x80000000 through 0xBFFFFFFF (that is, it is a privileged address). The control transfer to the service routine works slightly different for privileged and unprivileged addresses (see Chapter 2, Section ??). The service routine for TLB Miss Faults typically loads an appropriate mapping into the TLB, then executes the RFX instruction to restart the failed instruction. In terms of an overall mapping function, the TLB miss service routine moves the TLB to a different subset of the mapping function, such that the new subset contains the faulting address.

**9.4. TLB Entry Flags.** TLB entries may be flagged *valid* (the *valid* flag is set) or *invalid* (the *valid* flag is not set), and they may be flagged *writeable* (the *write* flag is set) or *write-protected* (the *write* flag is not set). These flags only come to effect in a TLB entry whose page number is found during a lookup. If the valid flag is not set for such an entry, then a *TLB Invalid Fault* is triggered. If the write flag is not set for such an entry and the access is a write access, then a *TLB Write Fault* is triggered. Otherwise, the access succeeds.

Note that the name of the *valid* flag is slightly misleading. The name might suggest that unsetting this flag marks a TLB entry as invalid and causes the lookup algorithm to overlook that entry. However, unsetting the *valid* flag actually marks the corresponding *page* as invalid and does not interfere with the lookup algorithm; instead, when the entry is found during lookup, it triggers a *TLB Invalid Fault*. To mark a TLB entry invalid and thus cause the lookup algorithm to overlook that entry, place an unused virtual page number into the entry, such as a page number from the direct-mapped virtual address range (0xC0000000 through 0xFFFFFFFF).

9.5. Random Replacement and Fixed TLB Entries. The TLB miss service routine typically replaces a TLB entry with a mapping for the faulting address, then restarts the faulting instruction. The question remains which entry to replace. The optimal strategy would be to modify the TLB in such a way that, out of the total  $(2^{20} - 2^{18})$  mappings, it contains the 32 entries most needed in the near future. It has been shown that replacing random entries moves towards that set quite quickly. Therefore, the ECO32 is designed to replace a random TLB entry easily, using a simple hardware random-number generator.

However, for certain purposes it is useful to exclude some TLB entries from being indexed by such random numbers. Therefore, the ECO32 has 4 fixed TLB entries at index 0..3, and 28 non-fixed TLB entries at index 4..31. Random replacement always chooses one of the non-fixed entries. The mapping stored in the fixed entries can only be changed by accessing them directly, i.e. not by random indexing.

**9.6. TLB Access Registers.** A set of special purpose registers is used to communicate with the TLB. The primary use for these registers is loading an entry into the TLB within a TLB Miss service routine. Another use would be to blank all TLB entries to move to a different overall mapping function. The TLB access registers are special-purpose registers that must be accessed with the MVFS and MVTS instructions. The special TBS, TBWR, TBRI, and TBWI instructions causes the actual operations between these registers and the TLB.

The purpose of these registers is as follows:

- the TLB Index Register contains the *Index* of an entry that is read with the next TLB read-by-index instruction (TBRI), written with the next TLB write-by-index instruction (TBWI), or found by the TLB search instruction (TBS). The index is a number in the range 0..31.

- the TLB Entry High Register contains the *high* part of an entry that was read or shall be written. The high part of an entry contains the virtual page number of that entry in the upper 20 bits. The lower 12 bits are ignored. After a *TLB Miss Fault*, *TLB Invalid Fault*, or *TLB Write Fault*, the TLB Entry High register contains the faulting page number.

- the TLB Entry Low Register contains the *low* part of an entry that was read or shall be written. The low part of an entry contains the physical page frame number of that entry in the upper 20 bits. It also contains the valid flag of that entry in bit 0, and the write-protection flag in bit 1. The remaining bits are ignored.

- the TLB Bad Address Register contains the faulting address after an Invalid Address Fault, Privileged Address Fault, TLB Miss Fault, TLB Invalid Fault, or TLB Write Fault.

# 10. Overall Memory Map

Taking all rules into account, the ECO32 distinguishes the following virtual address ranges:

- 0x00000000 through 0x7FFFFFFF: Page-mapped User Space

- 0x80000000 through 0xBFFFFFFF: Page-mapped Kernel Space

- $\bullet$  0xC0000000 through 0xDFFFFFFF: Direct-mapped Kernel Space, maps to RAM

- $\bullet$  0xE0000000 through 0xEFFFFFFF: Direct-mapped Kernel Space, maps to ROM

- 0xF0000000 through 0xFFFFFFFF: Direct-mapped Kernel Space, maps to peripheral devices

#### 11. Reset State

After a hardware reset, the ECO32 is in the following state:

- the general-purpose registers contain undefined values (except for register #0, which is not backed by a physical register, and always has the value 0).

- all bits of the PSW are set to 0, indicating in particular

- that the exception service routines are located at virtual addresses 0xE0000004 and 0xE0000008 (at the beginning of the ROM)

- that interrupts are globally disabled and that all interrupt channels are individually disabled

- that the ECO32 executes in Kernel Mode

- the PC is set to 0xE0000000, i.e. the first address in ROM. This location typically contains a jump instruction to escape the general exception service routine at 0xE0000004.

#### CHAPTER 3

# Instruction Set

The instructions of the ECO32 operate directly on the functional components described in the previous chapter. They can be subdivided into groups of instructions that work in a similar way:

- Computation: These instructions compute a function of values stored in general-purpose registers or encoded directly into the instruction and store the result in a general-purpose register.

- Control Flow: These instructions affect the PC in various ways.

- Load/Store: These instructions transfer data from or to RAM locations or peripheral device registers.

- System: Special instructions for PSW, MMU, or exception operation.

#### 1. Definitions

Some definitions are useful when explaining the effect of an instruction: An *immediate* value is a value encoded directly into the instruction. A *register value* is a 32-bit value taken from a general-purpose register. The interpretation of such values is up to the instruction.

A register value is referred to by an instruction by an immediate value that denotes the register number. If x is a 5-bit immediate value, then  $R_x$  shall denote the corresponding register value, and  $R_x \leftarrow \dots$  shall denote an assignment to this register. Similarly,  $S_i$  denotes special purpose register #i.  $R_{i,j}$  and  $S_{i,j}$  denote specific bits of a register. As a special rule, an assignment to  $R_0$  has no effect since that register is not writeable.

#### 2. General Execution Loop

The ECO32 executes the following loop to perform its task:

- Remember the current value of the PC register. If any exception occurs before the instruction is finished, this value is placed in register #30 such that the current instruction can be restarted.

- Load the current instruction from the virtual address stored in the PC. If that address is not word-aligned, then an *Invalid Address Exception* occurs. Otherwise, if it is a privileged address and the CPU is in user mode, then a *Privileged Address Exception* occurs. Otherwise, it is mapped to a physical address by the MMU, which may trigger a *TLB Miss Exception* or a *TLB Invalid Exception*. All these exceptions cause the faulting PC value to be stored in the *TLB Bad Address Register*. Note that a *TLB Write Exception* cannot occur since the instruction fetch is a read access.

- Increase the PC by 4.

- If the opcode in the instruction word does not denote a valid instruction, then an *Illegal Instruction Fault* is triggered.

- Decode and execute the instruction. Any fault triggered during this step immediately stops execution of the current instruction and transfers control to the fault service routine.

- Remember the new value of the PC register. If any interrupt occurs in the next step, this value is placed in register #30 such that control can return to the next instruction.

- Test for interrupts. If an interrupt is signalled and admitted (Chapter 2, Section ??), then control is transferred to the service routine (Chapter 2, Section ??).

### 3. Computation Instructions

The computation instructions compute a function of register values and/or immediate values, and store their result in a general-purpose register.

**3.1. ADD.** The ADD instruction computes the sum of two 32-bit register operands, truncated to 32 bits.

| Format: | Bits  | 3126   | 2521 | 2016 | 1511 | 100       |

|---------|-------|--------|------|------|------|-----------|

|         | Value | 000000 | X    | У    | r    | (ignored) |

|         |       |        |      |      |      |           |

Effect:

$$R_r \leftarrow truncate_{32}(R_x + R_y)$$

**3.2. ADDI.** The ADDI instruction computes the sum of a 32-bit register operand and a sign-extended 16-bit immediate operand, truncated to 32 bits.

| Format: | Bits  | 3126   | 2521 | 2016 | 150 |

|---------|-------|--------|------|------|-----|

| ronnat: | Value | 000001 | X    | r    | У   |

Effect:

$$R_r \leftarrow truncate_{32}(R_x + signext_{32}(y))$$

**3.3. SUB.** The SUB instruction computes the difference of two 32-bit register operands, truncated to 32 bits.

| Format: | Bits  | 3126   | 2521 | 2016 | 1511 | 100       |

|---------|-------|--------|------|------|------|-----------|

|         | Value | 000010 | X    | У    | r    | (ignored) |

Effect:

$$R_r \leftarrow truncate_{32}(R_x - R_y)$$

**3.4. SUBI.** The SUBI instruction computes the difference of a 32-bit register operand and a sign-extended 16-bit immediate operand, truncated to 32 bits.

| Format: | Bits  | 3126   | 2521 | 2016 | 150 |

|---------|-------|--------|------|------|-----|

| rormat: | Value | 000011 | X    | r    | У   |

$$R_r \leftarrow truncate_{32}(R_x - signext_{32}(y))$$

**3.5. MUL.** The MUL instruction computes the signed product of two 32-bit register operands, truncated to 32 bits.

| Format: | Bits  | 3126   | 2521 | 2016 | 1511 | 100       |

|---------|-------|--------|------|------|------|-----------|

| ronnat. | Value | 000100 | X    | У    | r    | (ignored) |

Effect:

$$R_r \leftarrow truncate_{32}(R_x *_{signed} R_y)$$

${\bf 3.6.}$  MULI. The MULI instruction computes the signed product of a 32-bit register operand and a sign-extended 16-bit immediate operand, truncated to 32 bits.

| Format: | Bits  | 3126   | 2521 | 2016 | 150 |

|---------|-------|--------|------|------|-----|

|         | Value | 000101 | X    | r    | У   |

Effect:

$$R_r \leftarrow truncate_{32}(R_x *_{signed} signext_{32}(y))$$

**3.7. MULU.** The MULU instruction computes the unsigned product of two 32-bit register operands, truncated to 32 bits.

| Format: | Bits  | 3126   | 2521 | 2016 | 1511 | 100       |

|---------|-------|--------|------|------|------|-----------|

| Format: | Value | 000110 | X    | У    | r    | (ignored) |

| Dr.     |       |        |      |      |      |           |

Effect:

$$R_r \leftarrow truncate_{32}(R_x *_{unsigned} R_y)$$

**3.8. MULUI.** The MULUI instruction computes the unsigned product of a 32-bit register operand and a zero-extended 16-bit immediate operand, truncated to 32 bits.

Effect:

$$R_r \leftarrow truncate_{32}(R_x *_{unsigned} zeroext_{32}(y))$$

**3.9. DIV.** The DIV instruction computes the signed quotient of two 32-bit register operands, truncated to 32 bits.

| Format: | Bits  | 3126   | 2521 | 2016 | 1511 | 100       |

|---------|-------|--------|------|------|------|-----------|

| Format: | Value | 001000 | X    | У    | r    | (ignored) |

Effect:

if

$$R_y = 0$$

then trigger a Division by Zero Fault  $R_r \leftarrow truncate_{32}(R_x/_{signed}R_y)$

**3.10. DIVI.** The DIVI instruction computes the signed quotient of a 32-bit register operand and a sign-extended 16-bit immediate operand, truncated to 32 bits.

| Format: | Bits  | 3126   | 2521 | 2016 | 1511 | 100       |

|---------|-------|--------|------|------|------|-----------|

| romat.  | Value | 001001 | X    | У    | r    | (ignored) |

if y = 0 then trigger a Division by Zero Fault

$R_r \leftarrow truncate_{32}(R_x/_{signed}signext_{32}(y))$

**3.11. DIVU.** The DIVU instruction computes the unsigned quotient of two unsigned 32-bit register operands, truncated to 32 bits.

Effect:

if  $R_y = 0$  then trigger a Division by Zero Fault  $R_r \leftarrow truncate_{32}(R_x/_{unsigned}R_y)$

**3.12. DIVUI.** The DIVUI instruction computes the unsigned quotient of a 32-bit register operand and a zero-extended 16-bit immediate operand, truncated to 32 bits.

Effect:

if y = 0 then trigger a Division by Zero Fault

$R_r \leftarrow truncate_{32}(R_x/_{unsigned}zeroext_{32}(y))$

**3.13. REM.** The REM instruction computes the signed remainder of two 32-bit register operands, truncated to 32 bits.

Effect:

if  $R_y = 0$  then trigger a Division by Zero Fault  $R_r \leftarrow truncate_{32}(R_x MOD_{signed}R_y)$

**3.14. REMI.** The REMI instruction computes the signed remainder of a 32-bit register operand and a sign-extended 16-bit immediate operand, truncated to 32 bits.

Effect:

if y = 0 then trigger a Division by Zero Fault

$R_r \leftarrow truncate_{32}(R_xMOD_{signed}signext_{32}(y))$

**3.15. REMU.** The REMU instruction computes the unsigned remainder of two unsigned 32-bit register operands, truncated to 32 bits.

Effect:

if  $R_y = 0$  then trigger a Division by Zero Fault

$R_r \leftarrow truncate_{32}(R_xMOD_{unsigned}R_y)$

**3.16. REMUI.** The REMUI instruction computes the unsigned remainder of a 32-bit register operand and a zero-extended 16-bit immediate operand, truncated to 32 bits.

| Format: | Bits  | 3126   | 2521 | 2016 | 1511 | 100       |

|---------|-------|--------|------|------|------|-----------|

| rormat. | Value | 001111 | X    | У    | r    | (ignored) |

Effect:

if y = 0 then trigger a Division by Zero Fault

$R_r \leftarrow truncate_{32}(R_xMOD_{unsigned}zeroext_{32}(y))$

**3.17. AND.** The AND instruction computes the bitwise AND of two 32-bit register operands.

| Format: Bits 3126 2521 201 | 0   1011 | 100       |

|----------------------------|----------|-----------|

| Value 010000 x y           | r        | (ignored) |

Effect:

$$R_{r,i} \leftarrow R_{x,i} \wedge R_{y,i}$$

**3.18. ANDI.** The ANDI instruction computes the bitwise AND of a 32-bit register operand and a zero-extended 16-bit immediate operand.

| Format: | Bits  | 3126   | 2521 | 2016 | 150 |

|---------|-------|--------|------|------|-----|

|         | Value | 010001 | X    | r    | У   |

|         |       |        |      |      |     |

Effect:

$$R_{r,i} \leftarrow R_{x,i} \wedge zeroext_{32}(y)_i$$

**3.19. OR.** The OR instruction computes the bitwise OR of two 32-bit register operands.

| Format: | Bits  | 3126   | 2521 | 2016 | 1511 | 100       |

|---------|-------|--------|------|------|------|-----------|

| roimat. | Value | 010010 | X    | У    | r    | (ignored) |

Effect:

$$R_{r,i} \leftarrow R_{x,i} \vee R_{y,i}$$

**3.20. ORI.** The ORI instruction computes the bitwise OR of a 32-bit register operand and a zero-extended 16-bit immediate operand.

| Format: | Bits  | 3126   | 2521 | 2016 | 150 |

|---------|-------|--------|------|------|-----|

| rormat. | Value | 010011 | X    | r    | У   |

Effect:

$$R_{r,i} \leftarrow R_{x,i} \lor zeroext_{32}(y)_i$$

**3.21. XOR.** The XOR instruction computes the bitwise XOR of two 32-bit register operands.

| Format: | Bits  | 3126   | 2521 | 2016 | 1511 | 100       |

|---------|-------|--------|------|------|------|-----------|

| ronnat. | Value | 010100 | X    | У    | r    | (ignored) |

$$R_{r,i} \leftarrow R_{x,i} \oplus R_{y,i}$$

**3.22. XORI.** The XORI instruction computes the bitwise XOR of a 32-bit register operand and a zero-extended 16-bit immediate operand.

| Format: | Bits  | 3126   | 2521 | 2016 | 150 |

|---------|-------|--------|------|------|-----|

| ronnat. | Value | 010101 | X    | r    | У   |

Effect:

$$R_{r,i} \leftarrow R_{x,i} \oplus zeroext_{32}(y)_i$$

**3.23. XNOR.** The XNOR instruction computes the bitwise XNOR of two 32-bit register operands.

| Format: | Bits  | 3126   | 2521 | 2016 | 1511 | 100       |

|---------|-------|--------|------|------|------|-----------|

| romat.  | Value | 010110 | X    | У    | r    | (ignored) |

Effect:

$$R_{r,i} \leftarrow \overline{R_{x,i} \oplus R_{y,i}}$$

**3.24. XNORI.** The XNORI instruction computes the bitwise XNOR of a 32-bit register operand and a zero-extended 16-bit immediate operand.

| Format: |       | 3126   | 2521 | 2016 | 150 |

|---------|-------|--------|------|------|-----|

| roimat. | Value | 010111 | x    | r    | У   |

| T .CC . |       |        |      |      |     |

Effect:

$$R_{r,i} \leftarrow \overline{R_{x,i} \oplus zeroext_{32}(y)_i}$$

**3.25. SLL.** The SLL instruction computes the result of shifting the first 32-bit register operand to the left by a number of bits specified by the 5 least significant bits of the second 32-bit register operand, and filling up with 0 bits.

Effect:

$$shift \leftarrow unsigned(R_{y,4..0})$$

$temp_i \leftarrow R_{x,i-shift} \text{ if } i \geq shift$

$temp_i \leftarrow 0 \text{ if } i < shift$

$R_r \leftarrow temp$

**3.26. SLLI.** The SLLI instruction computes the result of shifting the 32-bit register operand to the left by a number of bits specified by the 5 least significant bits of the immediate operand, and filling up with 0 bits.

$$shift \leftarrow unsigned(y_{4..0})$$

$temp_i \leftarrow R_{x,i-shift} \text{ if } i \geq shift$

$temp_i \leftarrow 0 \text{ if } i < shift$

$R_T \leftarrow temp$

**3.27. SLR.** The SLR instruction computes the result of shifting the first 32-bit register operand to the right by a number of bits specified by the 5 least significant bits of the second 32-bit register operand, and filling up with 0 bits.

Effect:

$$shift \leftarrow unsigned(R_{y,4..0})$$

$temp_i \leftarrow R_{x,i+shift} \text{ if } i+shift < 32$

$temp_i \leftarrow 0 \text{ if } i+shift \geq 32$

$R_r \leftarrow temp$

**3.28. SLRI.** The SLRI instruction computes the result of shifting the 32-bit register operand to the right by a number of bits specified by the 5 least significant bits of the immediate operand, and filling up with 0 bits.

Format: Bits 31..26 25..21 20..16 15..0

Value 011011 x r y

Effect:

$$shift \leftarrow unsigned(y_{4..0})$$

$temp_i \leftarrow R_{x,i+shift} \text{ if } i+shift < 32$

$temp_i \leftarrow 0 \text{ if } i+shift \geq 32$

$R_r \leftarrow temp$

**3.29. SAR.** The SAR instruction computes the result of shifting the first 32-bit register operand to the right by a number of bits specified by the 5 least significant bits of the second 32-bit register operand, and replicating the topmost (sign) bit.

Effect:

$$shift \leftarrow unsigned(R_{y,4..0})$$

$temp_i \leftarrow R_{x,i+shift} \text{ if } i+shift < 32$

$temp_i \leftarrow R_{x,31} \text{ if } i+shift \geq 32$

$R_r \leftarrow temp$

**3.30. SARI.** The SARI instruction computes the result of shifting the 32-bit register operand to the right by a number of bits specified by the 5 least significant bits of the immediate operand, and replicating the topmost (sign) bit.

$$shift \leftarrow unsigned(y_{4..0})$$

$temp_i \leftarrow R_{x,i+shift} \text{ if } i+shift < 32$

$temp_i \leftarrow R_{x,31} \text{ if } i+shift \geq 32$

$R_r \leftarrow temp$

**3.31. LDHI.** The LDHI instruction is used to generate large constants. The upper 16 bits of the result are taken from the 16-bit immediate operand. The lower 16 bits of the result are 0.

| Format: | Bits  | 3126   | 2521 | 2016 | 150 |

|---------|-------|--------|------|------|-----|

| roimat. | Value | 011111 | X    | r    | У   |

Effect:

$$R_{r,31..16} \leftarrow y_{15..0}$$

$R_{r,15..0} \leftarrow 0$

#### 4. Control Flow Instructions

Control flow instruction load immediate values or register values into the PC and/or load the value of the PC into a general-purpose register. The ECO32 supports unconditional *jumps*, conditional *branches*, indirect jumps, subroutine calls, subroutine returns, and indirect subroutine calls out of the box. More complex control flow schemes can be implemented by combining these instructions.

A control transfer is *conditional* if it only occurs on a certain condition that is computed from general-purpose registers. A control transfer is *unconditional* if it always occurs.

A control transfer is *direct* if the target address is supplied as an immediate value. It is *indirect* if the target address is supplied as a register value.

A control transfer is *absolute* if the value of the PC is overwritten with a totally new value. It is *relative* if the value of the PC is modified by adding or subtracting an offset.

Both relative control transfers and instructions that read the current PC value operate on the value of the PC after increasing it by 4 during instruction fetching.

**4.1. BEQ.** The BEQ instruction performs a conditional direct jump to a relative immediate sign-extended 16-bit offset counted as words. The condition is evaluated by comparing two 32-bit register operands and is asserted if the first operand is equal to the second operand.

Effect:

if

$$R_x = R_y$$

then  $PC \leftarrow PC + 4 * signext_{32}(offset)$

**4.2. BNE.** The BNE instruction performs a conditional direct jump to a relative immediate sign-extended 16-bit offset counted as words. The condition is evaluated by comparing two 32-bit register operands and is asserted if the first operand is not equal to the second operand.

|         | _     |        | _    |      |        |

|---------|-------|--------|------|------|--------|

| Format: | Bits  | 3126   | 2521 | 2016 | 150    |

|         | Value | 100001 | X    | У    | offset |

| Effect: |       |        |      |      |        |

if

$$R_x \neq R_y$$

then  $PC \leftarrow PC + 4 * signext_{32}(offset)$

**4.3. BLE.** The BLE instruction performs a conditional direct jump to a relative immediate sign-extended 16-bit offset counted as words. The condition is evaluated by comparing two 32-bit register operands and is asserted if the first operand is less or equal to (by signed comparison) the second operand.

Effect:

if  $R_x \leq_{signed} R_y$  then  $PC \leftarrow PC + 4 * signext_{32}(offset)$

**4.4. BLEU.** The BLEU instruction performs a conditional direct jump to a relative immediate sign-extended 16-bit offset counted as words. The condition is evaluated by comparing two 32-bit register operands and is asserted if the first operand is less or equal to (by unsigned comparison) the second operand.

Effect:

if  $R_x \leq_{unsigned} R_y$  then  $PC \leftarrow PC + 4 * signext_{32}(offset)$

**4.5. BLT.** The BLT instruction performs a conditional direct jump to a relative immediate sign-extended 16-bit offset counted as words. The condition is evaluated by comparing two 32-bit register operands and is asserted if the first operand is less than (by signed comparison) the second operand.

Effect:

if  $R_x <_{signed} R_y$  then  $PC \leftarrow PC + 4 * signext_{32}(offset)$

**4.6. BLTU.** The BLTU instruction performs a conditional direct jump to a relative immediate sign-extended 16-bit offset counted as words. The condition is evaluated by comparing two 32-bit register operands and is asserted if the first operand is less than (by unsigned comparison) the second operand.

Format: Bits | 31..26 | 25..21 | 20..16 | 15..0 | Value | 100101 | x | y | offset

Effect:

if  $R_x <_{unsigned} R_y$  then  $PC \leftarrow PC + 4 * signext_{32}(offset)$

**4.7. BGE.** The BGE instruction performs a conditional direct jump to a relative immediate sign-extended 16-bit offset counted as words. The condition is evaluated by comparing two 32-bit register operands and is asserted if the first operand is greater or equal to (by signed comparison) the second operand.

Effect:

if  $R_x \geq_{signed} R_y$  then  $PC \leftarrow PC + 4 * signext_{32}(offset)$

**4.8. BGEU.** The BGEU instruction performs a conditional direct jump to a relative immediate sign-extended 16-bit offset counted as words. The condition is evaluated by comparing two 32-bit register operands and is asserted if the first operand is greater or equal to (by unsigned comparison) the second operand.

if  $R_x \ge_{unsigned} R_y$  then  $PC \leftarrow PC + 4 * signext_{32}(offset)$

**4.9. BGT.** The BGT instruction performs a conditional direct jump to a relative immediate sign-extended 16-bit offset counted as words. The condition is evaluated by comparing two 32-bit register operands and is asserted if the first operand is greater than (by signed comparison) the second operand.

| Format: | Bits  | 3126   | 2521 | 2016 | 150    |

|---------|-------|--------|------|------|--------|

| roimat. | Value | 101000 | X    | У    | offset |

|         |       |        |      |      |        |

Effect:

if

$$R_x >_{signed} R_y$$

then  $PC \leftarrow PC + 4 * signext_{32}(offset)$

**4.10. BGTU.** The BGTU instruction performs a conditional direct jump to a relative immediate sign-extended 16-bit offset counted as words. The condition is evaluated by comparing two 32-bit register operands and is asserted if the first operand is greater than (by unsigned comparison) the second operand.

| Format: | Bits  | 3126   | 2521 | 2016 | 150    |

|---------|-------|--------|------|------|--------|

| romat.  | Value | 101001 | X    | У    | offset |

Effect:

if

$$R_x >_{unsigned} R_y$$

then  $PC \leftarrow PC + 4 * signext_{32}(offset)$

**4.11. J.** The J instruction performs an unconditional direct jump to a relative immediate sign-extended 26-bit offset counted as words.

| Format: | Bits  | 3126   | 250    |

|---------|-------|--------|--------|

| ronnat. | Value | 101010 | offset |

Effect:

$$PC \leftarrow PC + 4 * signext_{32}(offset)$$

**4.12. JR.** The JR instruction performs an unconditional indirect jump to an absolute offset stored in a general-purpose register. It can be used for simple indirect jumps as well as to return from a subroutine.

Effect:

$$PC \leftarrow R_{dest}$$

**4.13. JAL.** The JAL instruction stores the current PC value in register #31, then performs an unconditional direct jump to a relative immediate sign-extended 26-bit offset counted as words. It is primarily used for subroutine calls.

Effect:

$$R_{31} \leftarrow PC$$

$PC \leftarrow PC + 4 * signext_{32}(offset)$

**4.14. JALR.** The JALR instruction remembers the current PC value, then performs an unconditional indirect jump to an absolute offset stored in a general-purpose register. The previous PC value is then stored in register #31. It is primarily used for indirect subroutine calls, such as virtual method invocations in object-oriented programming.

$returnAddress \leftarrow PC$   $PC \leftarrow R_{dest}$   $R_{31} \leftarrow returnAddress$

#### 5. Load and Store Instructions

Load and store instructions transfer data from and to RAM and peripheral devices. All load/store instructions first compute a virtual address by adding a sign-extended 16-bit immediate value to a register value. That address is then transformed to a physical address by the MMU. The load/store operation is sent to the SoC bus using the physical address and responded to by a slave device attached to the bus. Both the slave device itself and the target location inside that device are determined from the physical address. A write operation stores a value in a RAM location or device register, but may also trigger side-effects in some devices. Similarly, a read operation reads a value from a RAM location or device register, but may also trigger side-effects in some devices. Write operations take the data to write from a general-purpose register. Read operations store the received data in a general-purpose register.

All load/store operations must be aligned to the transferred data size. If a half-word (word) sized load/store operation is not half-word (word) aligned, it triggers an *Illegal Address Fault*.

All virtual addresses in the range  $80000000_h$  through FFFFFFF<sub>h</sub> are privileged addresses and may only be accessed while in Kernel Mode. If such an address is accessed in User Mode, a *Privileged Address Fault* occurs.

The transformation of a virtual address to a physical address is done by the MMU and may trigger a *TLB Miss Fault*, *TLB Invalid Fault* or *TLB Write Fault*. The service routine for these kinds of faults typically restarts the load/store operation after fixing the problem.

Any of these exceptions – Illegal Address Fault, Privileged Address Fault, TLB Miss Fault, TLB Invalid Fault and TLB Write Fault – causes the faulting address to be loaded into the TLB Bad Address Register  $(S_4)$ .

Certain physical addresses may not actually correspond to any device attached to the SoC bus. This includes *holes* in the physical address map as well as the range of unused physical addresses  $(40000000_h \text{ through FFFFFFF}_h)$ . Access to such addresses results in a *Bus Timeout Fault*.

Load/store operations come in variants with different transfer size. Only the RAM and ROM support half-word and byte sized operations. Peripheral devices only support word-sized operations. Accessing peripheral devices with half-word or byte sized operations has an undefined effect. Access to RAM or ROM with different transfer sizes provides word-sized, half-word sized, and byte-sized views on the same memory locations. These views are arranged in a big-endian fashion.

When a half-word or byte sized location in RAM or ROM is read, the resulting value is extended to 32 bits to fit into a general-purpose register. Half-word and byte sized load operations come in variants that either sign-extend or zero-extend these values.

**5.1. LDW.** The LDW instruction reads a word-sized value from RAM, ROM, or a peripheral device.

Effect:

$A_v \leftarrow R_x + signext_{32}(y)$

if  $A_v$  is not word aligned then

$S_4 \leftarrow A_v$

trigger a  $Illegal\ Address\ Fault$

end if

if  $A_{v,31} = 1$  and  $U_C = 1$  then

$S_4 \leftarrow A_v$

trigger a Privileged Address Fault

end if

$pageNumber \leftarrow A_{v,31..12}$

if no TLB entry exists for pageNumber then

$S_4 \leftarrow A_v$

trigger a TLB Miss Fault

end if

if the TLB entry for pageNumber does not have the valid bit set then

$S_4 \leftarrow A_v$

trigger a TLB Invalid Fault

end if

$A_p \leftarrow$  page frame number in the TLB entry for pageAddress send a load word request using the address  $A_p$  to the SoC bus if no response is received then trigger a  $Bus\ Timeout\ Fault$

$R_r \leftarrow \text{response value}$

**5.2. LDH.** The LDH instruction reads a half-word-sized value from RAM, ROM, or a peripheral device. The result is sign-extended to 32 bits.

| Format:                                | Bits  | 3126   | 2521 | 2016 | 150 |  |

|----------------------------------------|-------|--------|------|------|-----|--|

| rormat.                                | Value | 110001 | X    | r    | У   |  |

| Effect:                                |       |        |      |      |     |  |

| $A_n \leftarrow R_n + signext_{22}(u)$ |       |        |      |      |     |  |

$A_v \leftarrow R_x + signext_{32}(y)$  if  $A_v$  is not half-word aligned then  $S_4 \leftarrow A_v$  trigger a Illegal Address Fault end if if  $A_{v,31} = 1$  and  $U_C = 1$  then  $S_4 \leftarrow A_v$  trigger a Privileged Address Fault end if  $pageNumber \leftarrow A_{v,31...12}$  if no TLB entry exists for pageNumber then  $S_4 \leftarrow A_v$  trigger a TLB Miss Fault end if

if the TLB entry for pageNumber does not have the valid bit set then  $S_4 \leftarrow A_v$  trigger a TLB Invalid Fault

end if  $A_p \leftarrow$  page frame number in the TLB entry for pageAddress

send a load half-word request using the address  $A_p$  to the SoC bus if no response is received then trigger a Bus Timeout Fault  $R_r \leftarrow signext_{32}$  (response value)

**5.3. LDHU.** The LDHU instruction reads a half-word-sized value from RAM, ROM, or a peripheral device. The result is zero-extended to 32 bits.

| Format: | Bits  |        | 2521 | 2016 | 150 |

|---------|-------|--------|------|------|-----|

| romat.  | Value | 110010 | X    | r    | У   |

Effect:

et:

$$A_v \leftarrow R_x + signext_{32}(y)$$

if  $A_v$  is not half-word aligned then

$$S_4 \leftarrow A_v$$

trigger a  $\mathit{Illegal}\ \mathit{Address}\ \mathit{Fault}$  end if if  $A_{v,31} = 1$  and  $U_C = 1$  then

$$S_4 \leftarrow A_v$$

trigger a  $\mathit{Privileged}\ \mathit{Address}\ \mathit{Fault}$  end if

$$\mathit{pageNumber} \leftarrow A_{v,31...12}$$

if no TLB entry exists for  $\mathit{pageNumber}\ then$

$$S_4 \leftarrow A_v$$

trigger a  $\mathit{TLB}\ \mathit{Miss}\ \mathit{Fault}$  end if if the TLB entry for  $\mathit{pageNumber}\ does$  not have the  $\mathit{valid}\ bit$  set then

$$S_4 \leftarrow A_v$$

trigger a  $\mathit{TLB}\ \mathit{Invalid}\ \mathit{Fault}$  end if

$$A_p \leftarrow \mathit{page}\ \mathit{frame}\ \mathit{number}\ in\ the\ \mathit{TLB}\ \mathit{entry}\ \mathit{for}\ \mathit{pageAddress}$$

send a load half-word request using the address  $A_p$  to the SoC bus

if no response is received then trigger a Bus Timeout Fault

$R_r \leftarrow zeroext_{32}(\text{response value})$

**5.4. LDB.** The LDB instruction reads a byte-sized value from RAM, ROM, or a peripheral device. The result is sign-extended to 32 bits.

Effect:

$\begin{array}{l} A_v \leftarrow R_x + signext_{32}(y) \\ \text{if } A_{v,31} = 1 \text{ and } U_C = 1 \text{ then} \\ S_4 \leftarrow A_v \\ \text{trigger a } Privileged \ Address \ Fault \\ \text{end if} \\ pageNumber \leftarrow A_{v,31..12} \\ \text{if no TLB entry exists for } pageNumber \ \text{then} \\ S_4 \leftarrow A_v \\ \text{trigger a } TLB \ \textit{Miss Fault} \\ \text{end if} \\ \text{if the TLB entry for } pageNumber \ \text{does not have the } valid \ \text{bit set then} \\ S_4 \leftarrow A_v \\ \text{trigger a } TLB \ \textit{Invalid Fault} \\ \text{end if} \\ A_p \leftarrow \text{page frame number in the TLB entry for } pageAddress \\ \end{array}$

$A_p \leftarrow$  page frame number in the TLB entry for pageAddress send a load byte request using the address  $A_p$  to the SoC bus if no response is received then trigger a  $Bus\ Timeout\ Fault$   $R_r \leftarrow signext_{32}(\text{response value})$

**5.5. LDBU.** The LDBU instruction reads a byte-sized value from RAM, ROM, or a peripheral device. The result is zero-extended to 32 bits.

Effect:

$A_v \leftarrow R_x + signext_{32}(y)$  if  $A_{v,31} = 1$  and  $U_C = 1$  then  $S_4 \leftarrow A_v$  trigger a Privileged Address Fault end if  $pageNumber \leftarrow A_{v,31..12}$  if no TLB entry exists for pageNumber then  $S_4 \leftarrow A_v$  trigger a TLB Miss Fault end if if the TLB entry for pageNumber does not have the valid bit set then  $S_4 \leftarrow A_v$  trigger a TLB Invalid Fault end if

$A_p \leftarrow$  page frame number in the TLB entry for pageAddress send a load byte request using the address  $A_p$  to the SoC bus if no response is received then trigger a  $Bus\ Timeout\ Fault$   $R_r \leftarrow zeroext_{32}(response\ value)$

**5.6. STW.** The STW instruction writes a word-sized value to RAM, ROM, or a peripheral device.

| Format: | Bits  | 3126   | 2521 | 2016 | 150 |

|---------|-------|--------|------|------|-----|

| ronnat. | Value | 110101 | X    | r    | У   |

| T 00    |       |        |      |      |     |

Effect:

$A_v \leftarrow R_x + signext_{32}(y)$

if  $A_v$  is not word aligned then

$S_4 \leftarrow A_v$

trigger a Illegal Address Fault

end if

if  $A_{v,31} = 1$  and  $U_C = 1$  then

$S_4 \leftarrow A_v$

trigger a Privileged Address Fault

end if

$pageNumber \leftarrow A_{v,31..12}$

if no TLB entry exists for pageNumber then

$S_4 \leftarrow A_v$

trigger a TLB Miss Fault

end if

if the TLB entry for pageNumber does not have the valid bit set then

$S_4 \leftarrow A_v$

trigger a TLB Invalid Fault

nd if

if the TLB entry for pageNumber does not have the write bit set then

$S_4 \leftarrow A_v$

trigger a TLB Write Fault

end if

$A_p \leftarrow \text{page frame number in the TLB entry for } pageAddress$

send a store word request using the address  $A_p$  and data  $R_r$  to the SoC bus

if no response is received then trigger a  $Bus\ Timeout\ Fault$

**5.7. STH.** The STH instruction writes a half-word-sized value to RAM, ROM, or a peripheral device.

| Format: | Bits  | 3126   | 2521 | 2016 | 150 |

|---------|-------|--------|------|------|-----|

| ronnat. | Value | 110110 | X    | r    | У   |

Effect:

$A_v \leftarrow R_x + signext_{32}(y)$

if  $A_v$  is not half-word aligned then

$S_4 \leftarrow A_v$

trigger a  $Illegal\ Address\ Fault$

end if

if  $A_{v,31} = 1$  and  $U_C = 1$  then

$S_4 \leftarrow A_v$

trigger a Privileged Address Fault

end if

$pageNumber \leftarrow A_{v,31..12}$

if no TLB entry exists for pageNumber then

$S_4 \leftarrow A_v$

trigger a TLB Miss Fault

end if

if the TLB entry for pageNumber does not have the valid bit set then

$S_4 \leftarrow A_v$

trigger a TLB Invalid Fault

end if

if the TLB entry for pageNumber does not have the write bit set then

$S_4 \leftarrow A_v$

trigger a TLB Write Fault

end if

$A_p \leftarrow \text{page frame number in the TLB entry for } pageAddress$

send a store half-word request using the address  $A_p$  and data  $R_{r,15..0}$  to the SoC bus

if no response is received then trigger a Bus Timeout Fault

**5.8. STB.** The STB instruction writes a byte-sized value to RAM, ROM, or a peripheral device.

| empherar ( | device.            |                         |           |          |         |                                    |

|------------|--------------------|-------------------------|-----------|----------|---------|------------------------------------|

| Format:    | Bits               | 3126                    | 2521      | 2016     | 150     |                                    |

| roimat.    | Value              | 110111                  | X         | r        | У       |                                    |

| Effect:    |                    |                         |           |          |         | •                                  |

| $A_v$      | $\leftarrow R_x +$ | $signext_3$             | $_2(y)$   |          |         |                                    |

| if $A$     | $v_{v,31} = 1$     | and $U_C$ :             | = 1  then | 1        |         |                                    |

|            | $S_4 \leftarrow A$ | $4_v$                   |           |          |         |                                    |

|            | trigger            | a Privile               | ged Add   | ress Fau | lt      |                                    |

| end        | if                 |                         |           |          |         |                                    |

| pag        | $eNumb\epsilon$    | $er \leftarrow A_{v,3}$ | 112       |          |         |                                    |

| if no      | o TLB e            | entry exis              | ts for pa | geNumb   | ber the | n                                  |

|            | $S_4 \leftarrow A$ | $4_v$                   |           |          |         |                                    |

|            | trigger            | a TLB A                 | Aiss Fau  | lt       |         |                                    |

| end        | if                 |                         |           |          |         |                                    |

| if th      | ne TLB             | entry for               | pageNu    | mber dc  | es not  | have the <i>valid</i> bit set then |

|            | $S_4 \leftarrow A$ | $4_v$                   |           |          |         |                                    |

|            | trigger            | a TLB I                 | nvalid F  | ault     |         |                                    |

| end        | if                 |                         |           |          |         |                                    |

| if th      | ne TLB             | entry for               | pageNu    | mber dc  | es not  | have the <i>write</i> bit set then |

|            | $S_4 \leftarrow A$ | $4_v$                   |           |          |         |                                    |

|            | trigger            | a TLB V                 | Vrite Fa  | ult      |         |                                    |

| end        | if                 |                         |           |          |         |                                    |

|            |                    |                         |           |          |         |                                    |

bus if no response is received then trigger a Bus Timeout Fault

send a store byte request using the address  $A_p$  and data  $R_{r,7..0}$  to the SoC

$A_p \leftarrow \text{page frame number in the TLB entry for } pageAddress$

# 6. System Instructions

**6.1. TRAP.** The TRAP instruction triggers a *Trap Fault*. It is typically used by user programs to request action from the operating system.

System implementer's note: The fault mechanism causes general purpose register #30 to be loaded with the address of the faulting instruction, that is, the TRAP instruction itself. However, the fault service routine typically wants to return to the instruction immediately following the TRAP instruction, such that the TRAP is not executed again. This can be achieved by adding 4 to the return address in  $R_{30}$  in the service routine. See Chapter 2, Section ?? for details.

| Format: | Bits  | 3126   | 250       |

|---------|-------|--------|-----------|

|         | Value | 101110 | (ignored) |

| Effect: |       |        |           |

trigger a Trap Fault

**6.2. RFX.** The RFX instruction returns control from an exception service routine to the interrupted program. The return address is taken from general purpose register #30. The RFX instruction also restores the privilege mode and interrupt enable to the interrupted state by popping the topmost values of the corresponding state stacks in the PSW. See Chapter 2, Section ?? and Chapter 2, Section ?? for details.

Effect:

if  $U_C = 1$  then trigger a Privileged Instruction Fault

$PC \leftarrow R_{30}$

$I_C \leftarrow I_P$

$I_P \leftarrow I_O$

$U_C \leftarrow U_P$

$U_P \leftarrow U_O$

**6.3.** MVFS. The MVFS transfers the value of a special-purpose register into a general-purpose register. See Chapter 2, Section ?? for details on the special-purpose registers.

| Format: | Bits  | 3126   | 2521      | 2016 | 150 |

|---------|-------|--------|-----------|------|-----|

| roimat. | Value | 111000 | (ignored) | r    | Z   |

Effect:

if  $U_C = 1$  then trigger a Privileged Instruction Fault

If z does not denote a valid special-purpose register, then trigger an  $\mathit{Illegal}$   $\mathit{Instruction}$   $\mathit{Fault}$

$$R_r \leftarrow S_z$$

**6.4. MVTS.** The MVFS transfers the value of a general-purpose register into a special-purpose register. See Chapter 2, Section ?? for details on the special-purpose registers.

| 1 0     |       |        |           |      |     |

|---------|-------|--------|-----------|------|-----|

| Format: | Bits  | 3126   | 2521      | 2016 | 150 |

| rormat. | Value | 111001 | (ignored) | r    | Z   |

Effect:

if  $U_C = 1$  then trigger a Privileged Instruction Fault

If z does not denote a valid special-purpose register, then trigger an  $\mathit{Illegal}$   $\mathit{Instruction}$   $\mathit{Fault}$

$$S_z \leftarrow R_r$$

**6.5. TBS.** The TBS instruction searches the TLB for a mapping for a virtual address specified in the TLB Entry High register  $(S_2)$  and stores the resulting entry index in the TLB Index register  $(S_1)$ .

Effect:

if  $U_C = 1$  then trigger a Privileged Instruction Fault  $PageNumber \leftarrow S_{2,31..12}$

if the TLB contains an entry for PageNumber then

$S_1 \leftarrow \text{(the corresponding TLB entry index)}$

else

$$S_1 \leftarrow 80000000_h$$

Special cases: The TBS instruction will "find" a TLB entry that uses a page number in the direct-mapped virtual address space (C0000000 $_h$  through FFFFFFF $_h$ ) if the TLB Entry High register contains the corresponding page number. Normal address translation would not find such an entry since it always chooses direct mapping for such addresses.

**6.6. TBWR.** The TBWR instruction replaces a random TLB entry. First, the index of the entry to replace is determined as a random number in the range of non-fixed TLB entries (see Chapter 2, Section ??). Then, data from the TLB Entry High and Low registers ( $S_2$  and  $S_3$ ) is written into that TLB entry.

| Format: | Bits  | 3126   | 250       |

|---------|-------|--------|-----------|

| romat.  | Value | 111011 | (ignored) |

Effect:

if  $U_C = 1$  then trigger a Privileged Instruction Fault

X := (random MOD 28) + 4

TLB Entry  $\#X \leftarrow (S_3, S_2)$

**6.7. TBRI.** The TBRI instruction reads data from a TLB entry indicated by the TLB Index register  $(S_1)$  into the TLB Entry High and Low registers  $(S_2)$  and  $(S_3)$ .

Effect:

if  $U_C = 1$  then trigger a Privileged Instruction Fault

$X := S_1 \text{ MOD } 32$

$(S_3, S_2) \leftarrow \text{TLB Entry } \#X$

**6.8. TBWI.** The TBWI instruction writes data from the TLB Entry High and Low registers ( $S_2$  and  $S_3$ ) into a TLB entry indicated by the TLB Index register ( $S_1$ ).

Effect:

if  $U_C = 1$  then trigger a Privileged Instruction Fault

$X := S_1 \text{ MOD } 32$

TLB Entry  $\#X \leftarrow (S_3, S_2)$

#### CHAPTER 4

# Signal Interface

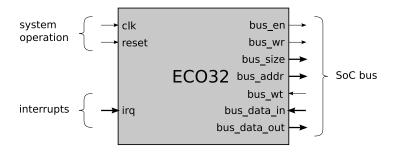

The signal interface to the ECO32 consists of three sets of signals:

- system operation signals: clock and reset

- SoC bus signals

- interrupt signals

FIGURE 1. ECO32 Signal Interface

## 1. System Operation Signals

Two system operation signals control the ECO32:

• The *clk* signal is a positive edge triggered clock signal that controls the timing of the ECO32. Since the ECO32 is a soft-core processor, minimum and maximum clock frequencies depend on the implementation in an FPGA and cannot be specified in general. The design of the ECO32 does not impose any particular constraints on the clock frequencies.

All other signals are synchronous to the *clk* signal.

• The reset signal is a positive level triggered clock-synchronous reset signal. If the reset is asserted, the ECO32 is placed into a partly defined reset state, as described in Chapter 2, Section ?? and execution is suspended until the reset is de-asserted. The ECO32 acts as an inactive master device with respect to the bus interface as long as the reset is asserted.

#### 2. Bus Architecture

The ECO32 can be connected to on-chip devices such as a RAM controller and other devices using a simple SoC bus architecture. The bus uses a synchronous handshake protocol with 32 address bits, 32 data bits, and byte-sized, half-word sized, or word-sized transfers.

Bus operation is divided into bus cycles. Each cycle guides a single transfer of a byte, half-word, or word value to or from the ECO32. All transfers are initiated by the ECO32 and responded to by other devices on the bus. For each transfer, the ECO32 emits an address that selects both a target device and a location inside that device. It also emits a signal that indicates whether it attempts to read data from that location, or write data to that location. It further emits a signal that indicates the transfer size. Finally, for write operations, the ECO32 also emits the data to write.

A bus request is responded to by a device with a signal that indicates success of the transfer. If the operation is a read operation, this signal also marks availability of the transferred data. If a certain amount of time passes without any device responding to the request, the transfer is considered failed, and a *Bus Timeout Fault* occurs.

**2.1. Bus Timing.** The operation of the SoC bus is synchronous with respect to the system clock. The bus architecture allows to complete a bus cycle with every clock cycle. Peripheral devices may slow down bus operation if they cannot respond fast enough.

A bus cycle begins by the ECO32 asserting the bus\_en signal to indicate the start of a transfer. At the same time, it emits the desired values on the bus\_wr, bus\_size, bus\_addr, and bus\_data\_out lines. The bus\_wr indicates a read cycle (if de-asserted) or a write cycle (if asserted). The bus\_size indicates the transfer size, with 10 or 11 indicating a word transfer, 01 indicating a half-word transfer, and 00 indicating a byte transfer. The bus\_addr is a 32-bit address signal group that selects both a peripheral device and a location in that device. Finally, bus\_data\_out indicates the transferred data in a write cycle. It is ignored in read cycles. All these signals must keep their value until the clock edge that marks the end of the bus cycle (see below).

The addressed device responds immediately, that is, in the same clock cycle in which the ECO32 asserted the bus request signals (with no intermediate clock edge), by placing a value on the bus\_wt line. Each positive clock edge that occurs while bus\_wt is asserted indicates a wait clock cycle and does not indicate the end of the bus cycle. This allows slower devices to perform internal operations. The device de-asserts bus\_wt as soon as its internal operations are finished. As soon as a positive clock edge occurs while bus\_wt is de-asserted, the bus cycle is finished. For read operations, the target device must assert the data to transfer prior to that clock edge, and keep it stable until after that clock edge. The clock cycle following that clock edge is no longer part of the bus cycle, and may witness the start of another bus cycle. Therefore, if the addressed device never asserts its bus\_wt signal, one bus cycle can be completed in each clock cycle.

If a physical address is emitted on the  $bus\_addr$  lines that is not associated with any device, then the bus itself keeps the  $bus\_wt$  line asserted permanently.

This eventually causes the ECO32 to trigger a *Bus Timeout Fault* and stop the bus cycle. A bus timeout is the only event that stops a bus cycle abnormally.

- **2.2.** Bus Address Map. The bus architecture places certain restriction on the mapping of physical addresses on the *bus\_addr* lines and addresses devices:

- Addresses in the range 0x00000000 through 0x1FFFFFFF are always associated with a RAM controller. However, only a subrange of these addresses are responded to if the RAM is smaller than 512 MB. RAM may be accessed with (aligned) word, half-word, or byte transfers.

- Addresses in the range 0x20000000 through 0x2FFFFFFF are always associated with a ROM controller. However, only a subrange of these addresses are responded to if the ROM is smaller than 256 MB. ROM may be accessed with (aligned) word, half-word, or byte transfers.